|

MiniSys CPU 结构

|

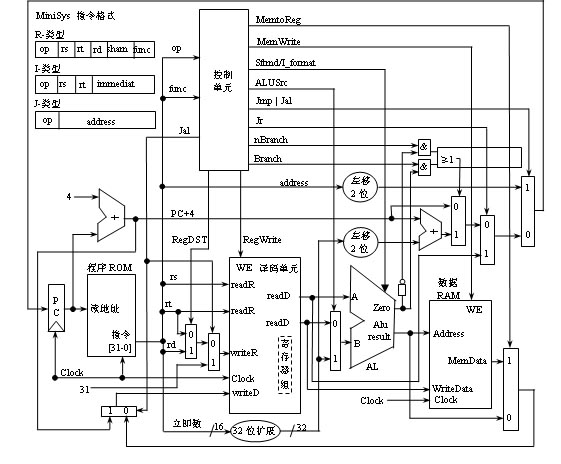

一个CPU的设计可以从指令集的设计开始,我们要设计的MiniSys CPU是一种RISC结构的CPU,在体系结构上主要借鉴了MIPS CPU,包括其寄存器组织方式以及指令集等。

根据指令在CPU中执行的流程,我们将指令在CPU中的执行过程分成四个基本步骤:取指、译码、执行和回写(或取数/存数)。

按照以上的四个步骤,整个CPU的内部功能被划分成5个基本单元:取指单元、译码单元、控制单元、执行单元和存储单元。

结构图如图2.1:

图2.1 结构图

由于本设计使用Altera公司的Cyclone FPGA芯片作为目标芯片,该芯片的内嵌RAM和内嵌ROM只支持同步存储器,同时寄存器的写入也需要时钟同步,所以图2.1中程序ROM、数据RAM和译码单元都有时钟信号clock输入端。除了时钟信号外,数据RAM还有WE输入端输入写允许信号;Address输入端输入读写RAM的地址;WriteData输入要写入的数据,而MemData输出从数据RAM读出的数据。

控制单元输出的控制信号及含义如表2.1所示。

表2.1 控制单元的输出信号

需要说明的是,图2.1的结构是初始CPU的结构,不包含中断处理和I/O访问等部分,在下一章,我们将对该结构进行必要的完善。

|

|

|